Original Link: https://www.anandtech.com/show/1634

IDF Spring 2005 - Day 2: The Yonah Scoop

by Anand Lal Shimpi on March 3, 2005 1:01 AM EST- Posted in

- Trade Shows

Sean Maloney alluded to a presentation by Intel's Mooly Eden, VP of Intel's Mobility Group and GM of Intel's Mobile Platforms Group. Although he wears a marketing hat these days, Mooly was the head of the design team of the original Pentium M (Banias) so he's an engineer at heart. The presentation was supposed to shed some more light on Intel's Yonah microprocessor, the dual core 65nm successor to Dothan.

In a brief conversation with Mooly before he got ready to speak, he reaffirmed that Yonah is much more than just two Dothans stuck together. While the same can't be said about the desktop Pentium D, when Mooly says something is more complex than people want to make it out to be, it usually is. Unfortunately architectural details about Yonah won't really be unveiled until later this year at the Fall IDF, despite that fact Mooly did provide some details on some of the more curious points brought up in this morning's presentation.

Mooly started out by saying that by the end of the year there will be over 150 Sonoma based Centrino systems, "but at IDF to speak about the present is the past." At which point he dove into discussion about Yonah.

Dual Core Pentium M - Why Wait?

The first question? Why wait until 2006 for a dual core Pentium M, when Intel is pushing for dual core in the desktop next quarter. The answer? It would simply be too big for a mobile platform, Yonah was designed from the start to be a 65nm processor, and thus it will have to wait until 2006.

On another somewhat related note, Mooly mentioned that the design of Yonah was started well before he left the Intel design center in Israel for the US, meaning that the Yonah team has been hard at work since before the launch of the original Pentium M.

The other main point that Mooly wanted to get across is that Yonah is far from two Dothans stuck together. We already know that Yonah features a shared 2MB L2 cache (shared by both cores), which is an initial indication that its not just two Dothans. But what else is there that sets Yonah apart from Dothan?

Making Pentium M more "Media Friendly"

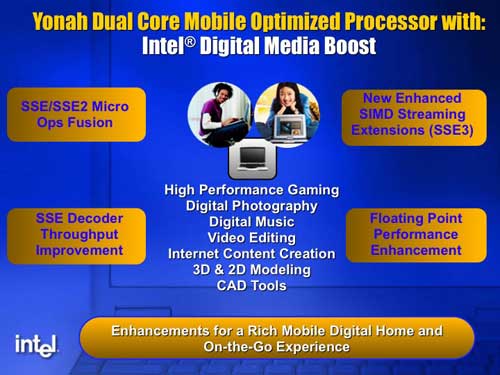

All of the major performance improvements to each of Yonah's cores seem to revolve around SIMD FP and FP performance, two of the Pentium M's present day weaknesses in comparison to the Pentium 4.

The first improvement is that now all three of Yonah's decoders can decode SSE instructions, regardless of the type of instruction. Improving the decode width of the processor is a quick way to improve performance.

Next, SSE/SSE2 operations (not sure if all can be, but at least some) can now be fused using the Micro Ops Fusion engine of Yonah. At a high level, the benefit here is increased performance and lower power consumption, we'll get into architectural details of why that is when we eventually sink our teeth into Yonah next year.

Each of the two cores in Yonah have also received support for SSE3 instructions much like the Pentium 4 E.

And finally there have been some improvements to Yonah's floating point performance, although Mooly would not say exactly what's been done. Curiously, Mooly referred to the floating point performance improvements as specifically made to improve gaming performance. Intel may have grander plans for Yonah than once thought...

The SSE/FP optimizations are all being grouped into what Intel is calling their Digital Media Boost technology, yes the names seem to get worse and worse as time goes on - but at least the functionality should be good.

Given that Yonah isn't going to a larger cache, the processor should have the same low latency 10 cycle 2MB L2 cache that we saw in Dothan, which is responsible for quite a bit of its performance. Combined with faster clock speeds (enabled by the 65nm process), dual core, a faster FSB and these "Digital Media" enhancements, Yonah may be a pretty solid competitor.

Dual Cores and Power Management

From the first time we heard the name Yonah we knew that its designers would be introducing some interesting power management technologies. While we don't normally like filling articles with quotes, here's one from Mooly today that is a great segway into this section:

"Yonah battery life will not be shorter than Dothan battery life...[it's] a huge achievement"

Given that Yonah will have twice the decode/execution transistors of Dothan, offering equal battery life for Yonah notebooks is a pretty impressive claim.

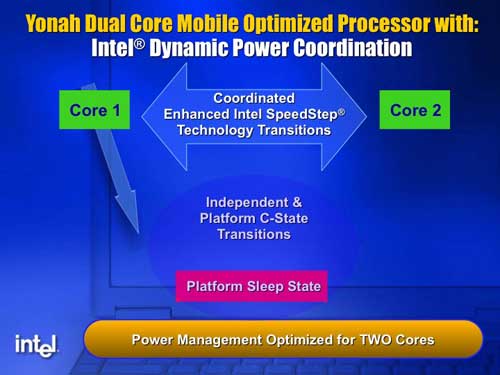

Mooly went through some of the power management technologies in Yonah that Intel is calling Dynamic Power Coordination. The idea is this - there are some areas where you can have each core operate independently with regards to reducing power consumption, but other areas where you can't.

Dothan has five operating states:

C0 - full power

C1 - auto halt (less power)

C2 - stop clock (even lower power)

C3 - sleep (lower power)

C4 - deep sleep (still lower)

The CPU's goal is to complete the tasks it's given, while always striving to be in as low of a power state as possible. So for example, if a Dothan is running an application that doesn't require full performance, it can operate in one of the lighter power saving states until it is done working, then eventually drop all the way down to C4.

The lighter power saving stages just do things like reduce clock speed or gate the clocks to parts of the chip, these types of things can be done independently on each core in Yonah (e.g. one core can be in C1 while the other core is in C0). Once you get down to adjusting voltage and playing with the PLL, then the two cores can't act independently - since they are both fed the same voltage and clock signal. Here is where Intel's Dynamic Power Coordination comes into play; if one CPU wants to go to a lower power state (e.g. C3 or C4) but the other core is running at C0, it will inform Intel's DPC logic of the current situation. Intel's logic, as you would expect it to act, will wait until the core running in C0 is done working and then move both cores down to the lower power state. Synchronization like this is important and it helps keep power consumption down to a minimum.

Because of the power management that is needed for Yonah, the two cores have to always work closely together to make sure that they are aware of each other's power state desires - for this reason alone Yonah is already much more than a pair of Dothans with a shared cache.

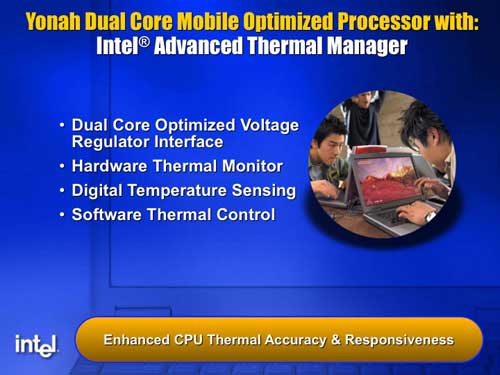

Yonah also introduces finer grained thermal management through what they are calling the Advanced Thermal Manager. With dedicated digital thermal sensors in each core, each with a higher accuracy, the temperature data the CPU can feed the rest of the system is more accurate in Yonah than in previous generation Pentium M CPUs. Although Mooly didn't talk about it here, you can expect that the thermal management technology in Yonah will allow for one core to be slowed down independently of the other if power consumption or heat dissipation rises too much.

Other Facts about Yonah

Mooly offered a few more tidbits of information about Yonah and the Napa platform:

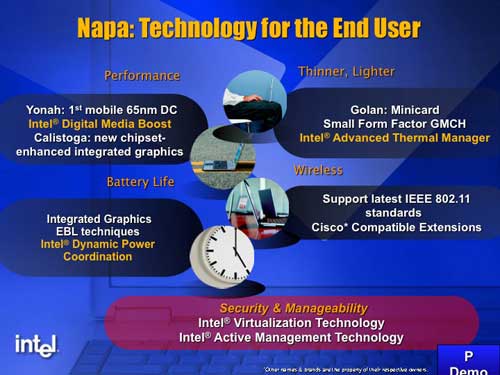

1) The Golan WiFi solution will be a minicard, less than half the size of the Colexico wireless solution used in current generation Pentium Ms. The WiFi in Napa will be 802.11a/b/g initially.

2) Yonah will have full support for Intel AMT and VT, both technologies we talked about yesterday.

3) The heat sink on the development Yonah platforms is purposefully large because the chip is far from mass production, the shipping chip will have no problems running just as cool, if not cooler than current generation Dothan notebooks.

4) No comment on EM64T support, although we doubt that Yonah will have 64-bit support out of the box. Remember that Yonah's execution units are borrowed from the Pentium 3, moving to 64-bit execution units would make the chip significantly larger, similar to what we saw in the Northwood -> Prescott transition (although not nearly as extreme, since the pipeline would remain the same). For a mobile platform, that decision just doesn't make sense yet.

5) The chipset is also listed as being a "Small Form Factor", most likely meaning that the package is smaller, allowing for even tinier board layouts.

Final Words

In meetings since Mooly's presentation we've been piecing together even more about the future of Yonah and Intel's strategy beyond Netburst, it looks like the focus on SIMD FP/FP performance was a calculated one...